# MULTI 8255/8253 CARD OPERATION MANUAL

# **CONTENTS:**

| CHAPTER 1 INTRODUCTION           | 1  |

|----------------------------------|----|

| CHAPTER 2 HARDWARE CONFIGURATION | 2  |

| CHAPTER 3 DATA SHEET             | 20 |

#### **CHAPTER 1 INTRODUCTION**

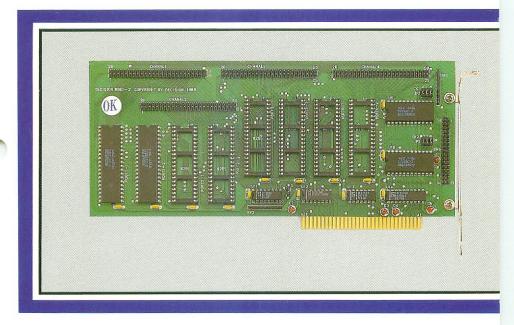

The multiple 8255 I/O card is a programmable peripheral interface for PC/XT, PC/AT or compatibles. The interface card provides 192 parallel input output (PIO) programmable line, and six independent 16 bits counter/clock.

#### The features of the multi-8255 I/O card are:

- \* Programmable I/O control functions.

- \* Up to 192 parallel I/O lines.

- \* Maximum of 2.35MHZ count rate.

- \* Six independent 16 bits counters.

- \* Support several operating modes which are programmable.

- \* Port address selectable.

# **CHAPTER 2 HARDWARE CONFIGURATION**

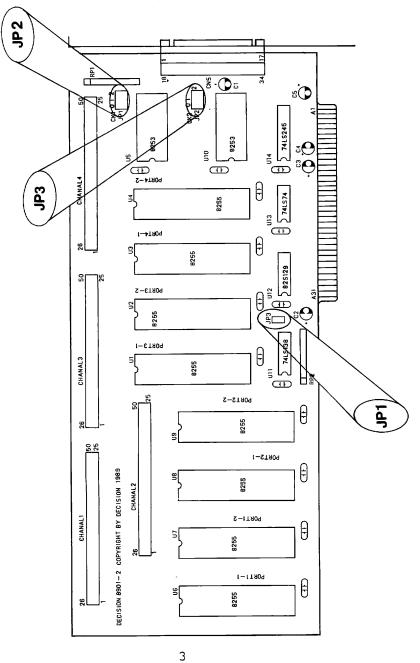

## 2.1 Configuration for jumpers setting

Before you use the multi-8255 I/O card, you must ensure that the I/O address and the clock are set correctly. Observe the figure belows the proper settings for the multi-8255 I/O card are described in the following:

# DECISION-COMPUTER International Co., Ltd.

# 1. I/O Address

The JP1 is used to select I/O port address, the address mapping of 8255 chips and 8253 chips are shown in the followings:

address mapping

| chip no. | JP1 short | JP1 open |

|----------|-----------|----------|

| 8255(1)  | 280-283   | 300-303  |

| 8255(2)  | 284-287   | 304-307  |

| 8255(3)  | 288-28B   | 308-30B  |

| 8255(4)  | 28C-28F   | 30C-30F  |

| 8255(5)  | 290-293   | 310-313  |

| 8255(6)  | 294-297   | 314-317  |

| 8255(7)  | 298-29B   | 318-31B  |

| 8255(8)  | 29C-29F   | 31C-31F  |

| 8253(1)  | 2A0-2A3   | 320-323  |

| 8253(2)  | 2A8-2AB   | 328-32B  |

JP1: Open

#### JP1

Select &H300 - &H32B as I/O port address. The I/O functions are shown in the following:

&H300: Port 1A input/output buffer.

&H301: Port 1B input/output buffer.

&H302: Port 1C input/output buffer.

&H303: Port 1 control register.

&H304: Port 2A input/output buffer.

&H305: Port 2B input/output buffer.

&H306: Port 2C input/output buffer.

&H307: Port 2 control register.

&H308: Port 3A input/output buffer.

&H309: Port 3B input/output buffer.

&H30A: Port 3C input/output buffer.

&H30B: Port 3 control register.

&H30C: Port 4A input/output buffer.

&H30D: Port 4B input/output buffer.

&H30E: Port 4C input/output buffer.

&H30F: Port 4 control register.

&H310: Port 5A input/output buffer.

&H311: Port 5B input/output buffer.

&H312: Port 5C input/output buffer.

&H313: Port 5 control register.

&H314: Port 6A input/output buffer.

&H315: Port 6B input/output buffer.

&H316: Port 6C input/output buffer.

&H317: Port 6 control register.

&H318: Port 7A input/output buffer.

&H319: Port 7B input/output buffer.

&H31A: Port 7C input/output buffer.

&H31B: Port 7 control register.

&H31C: Port 8A input/output buffer.

&H31D: Port 8B input/output buffer.

- &H31E: Port 8C input/output buffer.

- &H31F: Port 8 control register.

- &H320: Counter 1A input/output buffer.

- &H321: Counter 1B input/output buffer.

- &H322: Counter 1C input/output buffer.

- &H323: Counter 1 control register.

- &H328: Counter 2A input/output buffer.

- &H329: Counter 2B input/output buffer.

- &H32A: Counter 2C input/output buffer.

- &H32B: Counter 2 control register.

### JP1: Close (Default)

#### JP1

Select &H280 - &H2AB as I/O port address. The I/O functions are shown in the followings:

&H280: Port 1A input/output buffer.

&H281: Port 1B input/output buffer.

&H282: Port 1C input/output buffer.

&H283: Port 1 control register.

&H284: Port 2A input/output buffer.

&H285: Port 2B input/output buffer.

&H286: Port 2C input/output buffer.

&H287: Port 2 control register.

&H288: Port 3A input/output buffer.

&H289: Port 3B input/output buffer.

&H28A: Port 3C input/output buffer.

&H28B: Port 3 control register.

&H28C: Port 4A input/output buffer.

&H28D: Port 4B input/output buffer.

&H28E: Port 4C input/output buffer.

&H28F: Port 4 control register.

&H290: Port 5A input/output buffer.

&H291: Port 5B input/output buffer.

&H292: Port 5C input/output buffer.

&H293: Port 5 control register.

&H294: Port 6A input/output buffer.

&H295: Port 6B input/output buffer.

&H296: Port 6C input/output buffer.

&H297: Port 6 control register.

&H298: Port 7A input/output buffer.

&H299: Port 7B input/output buffer.

&H29A: Port 7C input/output buffer.

&H29B: Port 7 control register.

&H29C: Port 8A input/output buffer.

&H29D: Port 8B input/output buffer.

&H29E: Port 8C input/output buffer.

&H29F: Port 8 control register.

&H2A0: Counter 1A input/output buffer.

&H2A1: Counter 1B input/output buffer.

&H2A2: Counter 1C input/output buffer.

&H2A3: Counter 1 control register.

&H2A8: Counter 2A input/output buffer.

&H2A9: Counter 2B input/output buffer.

&H2AA: Counter 2C input/output buffer.

&H2AB: Counter 2 control register.

#### 2. Clock Selection

JP2 : JP2 is used to select clock of 8253(1).

#### JP2

1 2 3

.

. . .

JP2-1 = Short (default) :

Select internal clock to counter 1A.

JP2-2 = Short (default):

Select internal clock to counter 1B.

JP2-3 = Short (default):

Select internal clock to counter 1C.

JP2-1 = Open :

Select external clock to counter 1A.

JP2-2 = Open :

Select external clock to counter 1B.

JP2-3 = Open :

Select external clock to counter 1C.

JP3 : JP3 is used to select clock of 8253(2).

JP3

1 2 3

. . .

JP3-1 = Short (default):

Select internal clock to counter 2A.

JP3-2 = Short (default):

Select internal clock to counter 2B.

JP3-3 = Short (default):

Select internal clock to counter 2C.

JP3-1 = Open :

Select external clock to counter 2A.

JP3-2 = Open :

Select external clock to counter 2B.

JP3-3 = Open :

Select external clock to counter 2C.

#### 2.2 Hardware Installation

Your multi-8255 I/O card is designed to be inserted in any available slot in your PC/XT, PC/AT, or compatibles. In order to gain access to the expansion slots and the program switches on the mainboard, follow the steps listed below:

- 1. Set the multi-8255 I/O card switch.

- 2. Turn off all power of your computer and all peripheral devices before installing your multi-8255 I/O card.

- 3. Remove the cover of the computer.

- Insert your preconfigured card into any available slot. Make sure your I/O card is firmly seated in the chosen slot.

- 5. Replace the cover of the computer.

- 6. You are now ready to use your multi-8255 I/O card for several applications.

#### 2.3 Pin Assignment

There are four 50 pins I/O connectors, where CN1, CN2, CN3, CN4 corresponds to 8255 I/O ports, and CN5 corresponds to 8253 counter.

# CONNECTOR CN1 : 8255(U6) and 8255(U7)

|     |                            |                                      | <br> |                            |                                      |

|-----|----------------------------|--------------------------------------|------|----------------------------|--------------------------------------|

| PIN | 1<br>2<br>3<br>4<br>5      | 1PA0<br>1PA1<br>1PA2<br>1PA3<br>1PA4 | PIN  | 26<br>27<br>28<br>29<br>30 | GND<br>2PA0<br>2PA1<br>2PA2<br>2PA3  |

|     | 6<br>7<br>8<br>9           | 1PA5<br>1PA6<br>1PA7<br>1PB0<br>1PB1 |      | 31<br>32<br>33<br>34<br>35 | 2PA4<br>2PA5<br>2PA6<br>2PA7<br>2PB0 |

|     | 11<br>12<br>13<br>14       | 1PB2<br>1PB3<br>1PB4<br>1PB5<br>1PB6 | _    | 36<br>37<br>38<br>39<br>40 | 2PB1<br>2PB2<br>2PB3<br>2PB4<br>2PB5 |

|     | 16<br>17<br>18<br>19<br>20 | 1PB7<br>1PC0<br>1PC1<br>1PC2<br>1PC3 |      | 41<br>42<br>43<br>44<br>45 | 2PB6<br>2PB7<br>2PC0<br>2PC1<br>2PC2 |

|     | 21<br>22<br>23<br>24<br>25 | 1PC4<br>1PC5<br>1PC6<br>1PC7<br>GND  |      | 46<br>47<br>48<br>49<br>50 | 2PC3<br>2PC4<br>2PC5<br>2PC6<br>2PC7 |

# CONNECTOR CN2: 8255(U8) and 8255(U9)

| f:    |                                      |                                 |     |                            |                                      |

|-------|--------------------------------------|---------------------------------|-----|----------------------------|--------------------------------------|

| PIN   | 2 3P<br>3 3P<br>4 3P                 | PA0<br>PA1<br>PA2<br>PA3<br>PA4 | PIN | 26<br>27<br>28<br>29<br>30 | GND<br>4PA0<br>4PA1<br>4PA2<br>4PA3  |

|       | 7 3P<br>8 3P<br>9 3P                 | A5<br>A6<br>A7<br>B0<br>B1      | _   | 31<br>32<br>33<br>34<br>35 | 4PA4<br>4PA5<br>4PA6<br>4PA7<br>4PB0 |

|       | 11 3P<br>12 3P<br>13 3P<br>14 3P     | B3<br>B4<br>B5                  |     | 36<br>37<br>38<br>39<br>40 | 4PB1<br>4PB2<br>4PB3<br>4PB4<br>4PB5 |

| 1 1   | .6 3P<br>.7 3P<br>.8 3P<br>.9 3P     | C0<br>C1<br>C2                  | •   | 41<br>42<br>43<br>44<br>45 | 4PB6<br>4PB7<br>4PC0<br>4PC1<br>4PC2 |

| 2 2 2 | 1 3P<br>2 3P<br>3 3P<br>4 3P<br>5 GN | C5<br>C6<br>C7                  | _   | 46<br>47<br>48<br>49<br>50 | 4PC3<br>4PC4<br>4PC5<br>4PC6<br>4PC7 |

# CONNECTOR CN3 : 8255(U1) and 8255(U2)

| PIN | 1<br>2<br>3<br>4<br>5      | 5PA0<br>5PA1<br>5PA2<br>5PA3<br>5PA4 | PIN | 26<br>27<br>28<br>29<br>30 | GND<br>6PA0<br>6PA1<br>6PA2<br>6PA3  |

|-----|----------------------------|--------------------------------------|-----|----------------------------|--------------------------------------|

|     | 6<br>7<br>8<br>9           | 5PA5<br>5PA6<br>5PA7<br>5PB0<br>5PB1 |     | 31<br>32<br>33<br>34<br>35 | 6PA4<br>6PA5<br>6PA6<br>6PA7<br>6PB0 |

|     | 11<br>12<br>13<br>14<br>15 | 5PB2<br>5PB3<br>5PB4<br>5PB5<br>5PB6 |     | 36<br>37<br>38<br>39<br>40 | 6PB1<br>6PB2<br>6PB3<br>6PB4<br>6PB5 |

|     | 16<br>17<br>18<br>19       | 5PB7<br>5PC0<br>5PC1<br>5PC2<br>5PC3 |     | 41<br>42<br>43<br>44<br>45 | 6PB6<br>6PB7<br>6PC0<br>6PC1<br>6PC2 |

|     | 21<br>22<br>23<br>24<br>25 | 5PC4<br>5PC5<br>5PC6<br>5PC7<br>GND  |     | 46<br>47<br>48<br>49<br>50 | 6PC3<br>6PC4<br>6PC5<br>6PC6<br>6PC7 |

# CONNECTOR CN4 : 8255(U3) and 8255(U4)

| PIN | 1<br>2<br>3<br>4<br>5      | 7PA0<br>7PA1<br>7PA2<br>7PA3<br>7PA4 | PIN | 26<br>27<br>28<br>29<br>30 | GND<br>8PA0<br>8PA1<br>8PA2<br>8PA3  |

|-----|----------------------------|--------------------------------------|-----|----------------------------|--------------------------------------|

|     | 6<br>7<br>8<br>9           | 7PA5<br>7PA6<br>7PA7<br>7PB0<br>7PB1 | -   | 31<br>32<br>33<br>34<br>35 | 8PA4<br>8PA5<br>8PA6<br>8PA7<br>8PB0 |

|     | 11<br>12<br>13<br>14<br>15 | 7PB2<br>7PB3<br>7PB4<br>7PB5<br>7PB6 |     | 36<br>37<br>38<br>39<br>40 | 8PB1<br>8PB2<br>8PB3<br>8PB4<br>8PB5 |

|     | 16<br>17<br>18<br>19       | 7PB7<br>7PC0<br>7PC1<br>7PC2<br>7PC3 |     | 41<br>42<br>43<br>44<br>45 | 8PB6<br>8PB7<br>8PC0<br>8PC1<br>8PC2 |

|     | 21<br>22<br>23<br>24<br>25 | 7PC4<br>7PC5<br>7PC6<br>7PC7<br>GND  |     | 46<br>47<br>48<br>49<br>50 | 8PC3<br>8PC4<br>8PC5<br>8PC6<br>8PC7 |

# CONNECTOR CN5 : 8253(U5) and 8253(U10)

| PIN 1 2 3 4 5              | GND<br>1ACK<br>1AGAT<br>1AOUT<br>GND   | PIN | 26<br>27<br>28<br>29<br>30 | +5V<br>GND<br>-5V<br>GND<br>+12V |

|----------------------------|----------------------------------------|-----|----------------------------|----------------------------------|

| 6<br>7<br>8<br>9           | 1BCK<br>1BGAT<br>1BOUT<br>GND<br>1CCK  | -   | 31<br>32<br>33<br>34       | GND<br>-12V<br>GND<br>GND        |

| 11<br>12<br>13<br>14<br>15 | 1CGAT<br>1COUT<br>GND<br>2ACK<br>2AGAT |     |                            |                                  |

| 16<br>17<br>18<br>19<br>20 | 2AOUT<br>GND<br>2BCK<br>2BGAT<br>2BOUT |     |                            |                                  |

| 21<br>22<br>23<br>24<br>25 | GND<br>2CCK<br>2CGAT<br>2COUT<br>GND   |     |                            |                                  |

#### **CHAPTER 3 DATA SHEET**

The 8253 and 8255 data sheet are list in the following:

# FUNCTIONAL DESCRIPTION General

Tito b253 is a programmable interval timer/counter specifically designed for use with the Intel<sup>®</sup> Microcomputer systems. Its function is that of a general purpose, multi-timing element that can be treated as an array of I/O ports in the system software.

The 8253 solves one of the most common problems in any microcomputer system, the generation of accurate time delays under software control, instead of setting up timing loops in systems software, the programmer configures the 8253 to match his requirements, initializes one of the counters of the 8253 with the desired quantity, then upon command the 8253 will count-out the delay and interrupt the CPU when it has completed its tasks. It is easy to see that the software overhead is minimal and that multiple delays can easily be maintained by assignment of priority levels.

Other counter/timer functions that are non-delay in nature but also common to most microcomputers can be implemented with the 8253.

- · Programmable Rate Generator

- Event Counter

- . Binary Rate Multiplier

- Real Time Clock

- Digital One-Shot

- . Complex Motor Controller

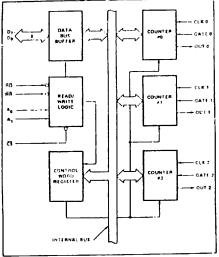

#### Data Bus Buffer

This 3-state, bi-directional, 8-bit buffer is used to interface the 8253 to the system data bus. Data is transmitted or received by the buffer upon execution of INput or OUTput CPU instructions. The Data Bus Buffer has three basic functions.

- 1. Programming the MODES of the 8253

- 2. Loading the count registers,

- 3. Reading the count values -

#### Read/Write Logic

The Read/Write Logic accepts inputs from the system bus and in turn generates control signals for overall device operation, it is enabled or disabled by CS so that no operation can occur to change the function unless the device has been selected by the system logic.

#### RD (Read)

A "low" on this input informs the 8253 that the CPU is inputting data in the form of a counters value.

#### WR (Write)

A "low" on this input informs the 8253 that the CPU is outputting data in the form of mode information or loading counters.

#### 40. A1

These inputs are normally connected to the address ous Their function is to select one of the three counters to be operated on and to address the control word register for mode selection.

#### CS (Chip Select)

A "low" on this input enables the 8253. No reading or writing will occur unless the device is selected. The CS input has no effect upon the actual operation of the counters.

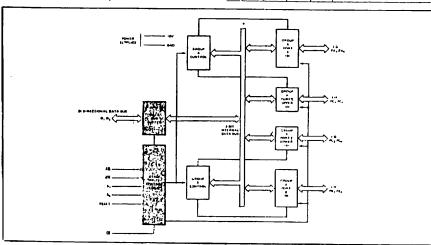

Figure 3. Block Diagram Showing Data Bus Buffer and Read/Write Logic Funations

| ČŠ | ŘĎ | WA | A, | Ao |                      |

|----|----|----|----|----|----------------------|

| 0  | 1  | 0  | 0  | 0  | Load Counter No. 0   |

| 0  | 1  | 0  | 0  | 1  | Load Counter No. 1   |

| 0  | 1  | 0  | 1  | 0_ | Load Counter No. 2   |

| 0  | 1  | 0  | 1  | 1  | Write Mode Word      |

| 0  | 0  | 1  | 0  | 0  | Read Counter No. 0   |

| 0  | 0  | 1  | 0  | 1  | Read Counter No. 1   |

| 0  | 0  | 1  | 1  | 0  | Read Counter No. 2   |

| 0  | 0  | 1  | 1  | 1  | No-Operation 3-State |

| 1  | X  | Х  | х  | X  | Disable 3-State      |

| 0  | 1  | 1  | X  | х  | No-Operation 3-State |

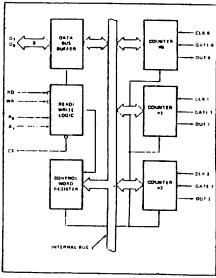

#### **Control Word Register**

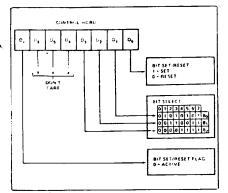

The Control Word Register is selected when A0. At are 11 it then accepts information from the data bus buffer and stores it in a register. The information stored in this register controls the operational MODE of each counter, selection of binary or BCD counting and the loading of each count register.

The Control Word Register can only be written into, no read operation of its contents is available

#### Counter #0, Counter #1, Counter #2

These three functional blocks are identical in operation so only a single. Counter will be described. Each Counter consists of a single. 16-bit, pre-settable. DOWN counter to counter can operate in either binary or BCD and its input, gate and output are configured by the selection of MODES stored in the Control Word Register.

The counters are fully independent and each can have separate Mode configuration and counting operation, binary or BCD. Also, there are special features in the control word that handle the loading of the count value so that software overhead can be minimized for these functions.

The reading of the contents of each counter is available to the programmer with simple READ operations for event counting applications and special commands and logic are included in the 8253 so that the contents of each counter can be read "on the fly" without having to inhibit the clock input.

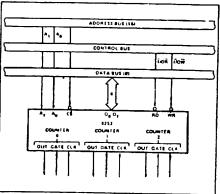

#### 8253 SYSTEM INTERFACE

The 8253 is a component of the Intel® Microcomputer Systems and Interfaces in the same manner as all other peripherals of the family. It is treated by the systems softwere as an array of peripheral I/O ports; three are counters and the fourth is a control register for MODE programming.

Basically, the select Inputs A0, A1 connect to the A0, A1 address bus signals of the CPU. The CS can be derived directly from the address busing a linear select method. Or it can be connected to the output of a decoder, such as an Intel® 8205 for larger systems.

Figure 4. Block Diagram Showing Control Word

Register and Counter Functions

Figure 5. 8253 System Interface

#### OPERATIONAL DESCRIPTION

#### General

The complete functional definition of the 8253 is programmed by the systems software. A set of control words must be sent out by the CPU to faritialize each counter of the 8253 with the destried MODE and quantity information. Prior to initialization, the MODE, count, and output of all counters is undefined. These control words program the MODE, Loading sequence and selection of binary or BCD counting.

Once programmed, the 8253 is ready to perform whatever timing tasks it is assigned to accomplish.

The actual counting operation of each counter is completely independent and additional logic is provided on-chip so that the usual problems associated with efficient monitoring and management of external, asynchronous events or rates to the inicrocomputer system have been eliminated.

#### Programming the 8253

All of the MCDES for each counter are programmed by the systems software by simple I/O operations

Each counter of the 8253 is individually programmed by writing a control word into the Control Word Register. (A0, A1 ± 11)

#### Control Word Format

|                  |     |     | D <sub>4</sub> |    |    |    |     |   |

|------------------|-----|-----|----------------|----|----|----|-----|---|

| S <sup>C</sup> 1 | SC0 | RL1 | RLO            | M2 | М1 | МО | BCD | l |

#### **Belinition of Control**

#### SC - Select Counter

| SC1 | SC0 |                  |

|-----|-----|------------------|

| U   | 0   | Select/Counter 0 |

| 0   | 1   | Select Counter 1 |

| 1   | С   | Select Counter 2 |

| 1   | 1   | Illegal          |

#### RL - Read/Load:

|    |   | _ |   |   |

|----|---|---|---|---|

| RL | } | R | L | Į |

| N.C. | N.L.O |                                                                     |

|------|-------|---------------------------------------------------------------------|

| 0    | 0     | Counter Latching operation (see READ/WRITE Procedure Section)       |

| J    | U     | Read/Load most significant byte only                                |

| 0    | 1     | Read/Load least significant byte only.                              |

| 1    | ١     | Read/Load least significant byte first, then most significant byte. |

#### M - MODE:

#### M2 M1 M0

| 0 | 0 | T | 0 | Mode 0 |

|---|---|---|---|--------|

| 0 | 0 | Т | 1 | Mode 1 |

| 1 | 1 | T | 0 | Mode 2 |

| 1 | 1 | T | 1 | Mode 3 |

| C | 0 | T | 0 | Mode 4 |

| C | 0 | T | 1 | Mode 5 |

#### BCD:

| 0 | Binary Counter 16-bits                            |

|---|---------------------------------------------------|

| 1 | Binary Coded Decimal (BCD) Counter<br>(4 Decades) |

#### Counter Loading

The count register is not loaded until the count value is written (one or two bytes, depending on the mode selected by the RL bits), followed by a rising edge and a falling edge of the clock. Any read of the counter prior to that falling clock edge may yield invalid date.

#### **MODE Delinition**

MODE 0: Interrupt on Terminal Count. The output will be initially low after the mode set operation. After the count is loaded into the selected count register, the output will remain low and the counter will count. When terminal count is reached the output will go high and remain high until the selected count register is reloaded with the mode or a new count is loaded. The counter continues to decrement after terminal count has been reached.

Rewriting a counter register during counting results in the following:

- (I) Write 1st byte stops the current counting.

- (2) Write 2nd byte starts the new count.

MODE 1: Programmable One-Shot. The output will go low on the count following the rising edge of the gate input.

The output will go high on the terminal count, if a new count value is loaded while the output is low it will not affect the duration of the one-shot pulse until the succeeding trigger. The current count can be read at any time without affecting the one-shot pulse.

The one-shot is retriggerable, hence the output lift remain low for the full count after any rising edru of the gate input. MODE 2: Rate Generator. Divide by N counter. The output will be low for one period of the input clock. The period from one output pulse to the next equals the number of input counts in the count register. If the count register is reloaded between output pulses the present period will not be affected, but the subsequent period will reflect the new value.

The gate input, when low, will force the output high. When the gate input goes high, the counter will start from the initial count. Thus, the gate input can be used to synchronize the counter.

When this mode is set, the output will remain high until after the count register is loaded. The output then can also be synchronized by software.

MODE 3: Square Wave Rate Generator. Similar to MODE 2 except that the output will remain high until one half the count has been completed (for even numbers) and go low for the other half of the count. This is accomplished by decrementing the counter by two on the falling edge of each clock pulse. When the counter reaches terminal count, the state of the output is changed and the counter is reloaded with the full count and the whole process is repeated.

If the count is odd and the output is high, the first clock pulse (after the count is loaded) decrements the count by 1. Subsequent clock pulses decrement line clock by 2. After timeout, the output goes low and the full count is reloaded. The first clock pulse (following the reload) decrements the counter by 3. Subsequent clock pulses decrement the count by 2 until timeout. Then the whole process is repeated. In this way, if the count is odd, the output will be high for (N + 1)/2 counts and low for (N - 1)/2 counts.

MODE 4: Software Triggered Strobe, After the mode is set, the output will be high. When the count is loaded, the counter will begin counting. On terminal count, the

output will go low for one input clock period, then will go high again..

If the count register is reloaded during counting, the new count will be loaded on the next CLK pulse. The count will be inhibited while the GATE input is low.

MODE 5: Hardware Triggered Strobe. The counter will start counting after the rising edge of the trigger Input and will go low for one clock period when the terminal count is reached. The counter is retriggerable. The output will not go low until the full count after the rising edge of any trigger.

| Modes | Signal<br>Slatus | Law<br>Or Going<br>Low                                         | Rising                                                        | High                |

|-------|------------------|----------------------------------------------------------------|---------------------------------------------------------------|---------------------|

| e     |                  | Disables counting                                              |                                                               | Enables<br>counting |

| 1     |                  |                                                                | initiates     counting     Resets output     after next clack |                     |

| 2     |                  | Disables     counting     Sets output     immediately     high | 1) Reloads counter 2) Initiates counting                      | Enables<br>counting |

| 3     |                  | Disables     counting     Sets output     Immediately     high | Initiales<br>Counling                                         | Enables<br>counting |

| 4     |                  | Disables<br>counting                                           |                                                               | Enables<br>counting |

| 8     |                  |                                                                | Initiates<br>counting                                         |                     |

Figure 5. Gate Pin Operations Summary

#### 8253 READ/WRITE PROCEDURE

#### Write Operations

The systems software must program each counter of the 8253 with the mode and quantity desired. The programmer must write out to the 8253 a MODE control word and the programmed number of count register bytes (1 or 2) prior to actually using the selected counter.

The actual order of the programming is quite flexible Writing out of the MODE control word can be in any sequence of counter selection, e.g., counter 80 does not have to be first or counter 82 last. Each counter's MODE control word register has a separate address so that its loading is completely sequence independent (SCO, SCI).

The loading of the Count Register with the actual count value, however, must be done in exactly the sequence programmed in the MODE control word (RLO, RL1). This loading of the counter's count register is still sequence independent like the MODE control word toading, but when a selected count register is to be loaded it must be loaded with the number of bytes programmed in the MODE control word (RLO, RL1). The one or limb bytes to be abaded in the count register do not have to follow the associated MODE control word. They can be programmed at any time following the MODE control word toading as long as the correct number of bytes is loaded in order.

All counters are down counters. Thus, the value loaded into the count register will actually be decremented. Loading all zeroes into a count register will result in the maximum count (2°16) Binary or 10°16/8CC). In MODE 0 the new count will not restart until the load has been compreted. It will accept one of two bytes depending on how the MODE control words (RLO, RL1) are programmed. Then proceed with the restart operation.

|      | MODE Control Word Counter n      |

|------|----------------------------------|

| L\$8 | Count Register byte<br>Counter n |

| MSB  | Count Register byte<br>Counter n |

Note: Formet shown is a simple example of loading the 8253 and does not imply that it is the only formet that can be used.

Figure 8. Programming Format

|       |     |                                  | A1 | ΑO |

|-------|-----|----------------------------------|----|----|

| No. 1 |     | MODE Control Word Counter 0      | ,  | 1  |

| No. 2 |     | MODE Control Word Counter 1      | 1_ | 1  |

| No. 3 |     | MODE Control Word Counter 2      | 1  | 1  |

| No. 4 | LSB | Count Register Byte Counter 1    | 0  | 1  |

| No. 5 | MSB | Count Register Byte Counter 1    | 0  | ,  |

| No. 6 | LSB | Count Register Byle Counter 2    | 1  | 0  |

| No. 7 | MSB | Count Register Byte Counter 2    | 1  | 0  |

| No. 8 | LSB | Count Register Byte<br>Counter 0 | 0  | 0  |

| No. B | мѕв | Count Register Byte Counter 0    | 0  | 0  |

Note: The exclusive addresses of each counter's count register make the task of programming the 8253 a very cimple matter, and constitute site tive use of the device will result if this feature is fully utilized.

Figure 9. Alternate Programming Formats

#### Read Operations

In most countar applications it becomes necessary to read the value" of the count. In progress and make a computational decision based on this quantity. Event counters are probably the most common application that uses this function. The 8253 contains logic that will allow the programmer to easily read the contents of any of the linee counters without disturbing the actual count in progress.

There are two methods that the programmer can use to read the value of the counters. The first method involves the use of simple 1/0 read operations of the selected counter. By controlling the AQ, A1 inputs to the 8253 the programmer can select the bounter to be read (remember that no read operation of the mode register is allowed AQ, A1-11). The only requirement with this method is that in order to assure a stable counter ending the actual operation of the is selected counter must be inhibited either by controlling the Gate input or by external logic that inhibits the clock input. The contents of the counter selected will be available as follows:

first I/O Read contains the least significant byte (LSB) second I/O Read contains...the most significant byte (MSB)

Due to the Internal logic of the 8253 it is absolutely necessary to complete the entire reading procedure. If two bytes are programmed to be read then two bytes must be read before any loading WR command can be sent to the same counter.

#### Read Operation Chart

| A1 | AD | RD |                    |

|----|----|----|--------------------|

| 0  | 0  | 0  | Read Counter No. 0 |

| 0  | 1  | 0  | Read Counter No. 1 |

| 1  | 0  | 0  | Read Counter No. 2 |

| 1  | 1  | 0  | Illegal            |

#### Reading While Counting

In order for the programmer to read the contents of any counter without effecting or disturbing the counting operation the 8253 has special internal logic that can be accessed using simple WR commands to the MODE register Basically, when the programmer wishes to read the contents of a selected counter on the fly heloads the MODE register with a special code which talches the present count value into a storage register so that its contents contain, an accurate, stable quantity. The programmer then issues a normal read command to the selected counter and the contents of the latched register is available.

#### MODE Register for Latching Count

#### A0, A1 = 11

| D7  | D6  | 05 | D4 | D3 | D2 | DI | DO |

|-----|-----|----|----|----|----|----|----|

| SCI | SCO | 0  | 0  | ×  | Х  | Х  | х  |

SC1,SC0 - specify counter to be laiched.

D5.D4 - 00 designates counter latching operation

x - don't care.

The same limitation applies to this mode of reading the counter as the previous method. That is, it is mandatory to complete the entire read operation as programmed. This command has no effect on the counter's mode.

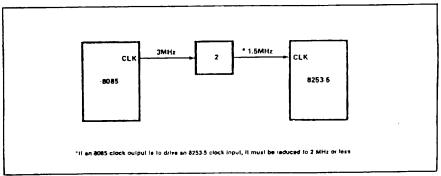

Figure 10. MCS-85" Clock Interface"

#### 8255A FUNCTIONAL DESCRIPTION

#### General

The 8255A is a programmable peripheral interlace (PPI) device designed for use in Intel® microcomputer systems, its function is that of a general purpose I/O component to injerface peripheral equipment to the microcomputer system bus. The functional configuration of the 8255A is programmed by the system software so that normally no external logic is necessary to interface peripheral devices or structures.

#### Data Bus Buffer

This 3-state bidirectional 8-bit buffer is used to interface the 8255A to the system date bus. Data is transmitted or received by the buffer upon execution of input or output instructions by the CPU. Control words and status information are also transferred through the data bus buffer.

#### Read/Write and Control Logic

The function of this block is to manage all of the internal and external transfers of both Data and Control or Status words. It accepts inputs from the CPU Address and Control busses and in turn, issues commands to both of the Control Groups.

#### (CS)

Chip Select, A "low" on this input pin enables the communiction between the 8255A and the CPU.

#### (RD)

Resd. A "low" on this input oin enables the 8255A to send the data or status information to the CPU on the data bus, in essence, it allows the CPU to "read from" the 8255A.

#### (WR)

Write. A "low" on this input pin enables the CPU to write data or control words into the 8255A.

#### (Ag and A<sub>1</sub>)

Port Select 0 and Port Select 1. These input signals, in conjunction with the RD and WR inputs, control the selection of one of the three ports or the control word registers. They are normally connected to the least significant bits of the address bus  $(A_0$  and  $A_1)$ .

#### 8255A BASIC OPERATION

| <u>A1</u> | A <sub>0</sub> | ÃĐ | WA | CS. | INPUT OPERATION (READ)      |

|-----------|----------------|----|----|-----|-----------------------------|

| 0         | 0              | 0  | 1  | 0   | PORT A - DATA BUS           |

| 0         | 1              | ٥  | 1  | 0   | PORT B - DATA BUS           |

| 1         | 0              | 0  | 1  | ٥   | PORT C - DATA BUS           |

|           |                |    |    |     | OUTPUT OPERATION<br>(WRITE) |

| 0         | 0              | 1  | 0  | 0   | DATA BUS - PORT A           |

| 0         | 1              | t  | 0  | 0   | DATA BUS - PORT B           |

| 1         | 0              | 1  | 0  | 0   | DATA BUS - PORT C           |

| 1         | 1              | 1  | 0  | 0   | DATA BUS - CONTROL          |

|           |                |    |    |     | DISABLE FUNCTION            |

| Х         | х              | х  | X  | 1   | DATA BUS - 3-STATE          |

| 1         | 1              | 0  | 1  | 0   | ILLEGAL CONDITION           |

| х         | X              | 1  | 1  | 0   | DATA BUS - 3-STATE          |

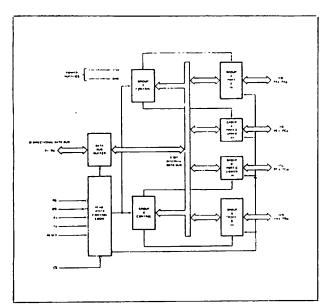

Figure 3. 8255A Block Diagram Showing Data Bus Buffer and Read/Write Control Logic Functions

#### (RESET)

Reset. A "high" on this input clears the control register and all ports (A, B, C) are set to the input mode

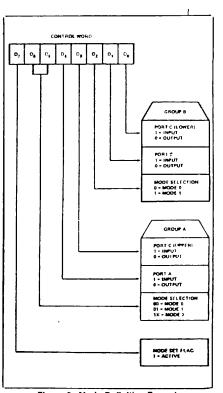

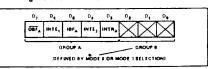

#### Group A and Group B Controls

The functional configuration of each port is programmed by the systems software. In essence, the CPU "outputs" a control word to the 8255A. The control word contains information such as "mode"; "bit set", "bit reset", stc., that initializes the functional configuration of the 8255A.

Each of the Control blocks (Group A and Group B) accepts "control to them the Road/Write Control Logic, receives "control words" from the internal data bus and issues the proper commands to its associated ports.

Control Group A = Port A and Port C upper IC7 C41 Control Group B =: Port B and Port C lower (C3 C0)

The Control Word Register can Only be written into. No Read oper tion of the Control Word Register is allowed.

#### Ports A, B, and C

The 8255A contains three 8 bit ports (A. B. and C). All can be configured in a wide variety of functional characteristics by the system software but each has its own special features or "personality" to further enhance the power and flexibility of the 8255A.

Port A. One 8 bit data output latch/buffer and one 8-bit data input latch.

Port B. One 8-bit data input/output latch/buffer and one 8-bit data input buffer.

Port C. One 8-bil data output latch/buller and one 8-bit data input buffer (no latch for input). This port can be divided into two 4-bit ports under the mode control. Each 4-bit port contains a 4-bit latch and it can be used for the control signal outputs and status signal inputs in conjunction with ports A and B.

Figure 4. 8225A Block Diagram Showing Group A and Group B Control Functions

#### PIN CONFIGURATION

| **1[  | ·   | $\bigcirc$ | \$  |         |

|-------|-----|------------|-----|---------|

| *** [ | ,   |            | 74  | b •••   |

| *** [ | ,   |            | ж   | D ***   |

| ***!  | ١.  |            | ٠,, |         |

| ÃÔ "  | ١,  |            | 76  | ე ≂ ი   |

| G (   |     |            | - > | 7 -1116 |

| 0.0   | ١.  |            |     | ie.     |

| •• {  |     |            | "   | 10,     |

| 44 (  | •   |            | -11 | 10,     |

| ****  |     |            | -11 | 10,     |

| ***   |     | \$255A     | ×   | 10.     |

| ***   |     |            | 75  | 10,     |

| ***   | - 1 |            | **  | to.     |

| *c+1  |     |            | "   | ٠,      |

| PC: C | ١., |            | ~   | ٠ ٧,    |

| 1134  |     |            | -41 | ***     |

| PC 11 |     |            | 74  | 1 ***   |

| ***1  | ••  |            | "   | ; •••   |

| ***;  | ٠.  |            | "   | 1 ***   |

| 7071  | 20  |            | ··· | 1 ***   |

|       |     |            | '   |         |

#### PIN NAMES.

| 0, .0,   | CATA BUS IBI DIRECTIONAL |

|----------|--------------------------|

| RESET    | ACSET NPUT               |

| 3        | CHIP SELECT              |

| A.C.     | READ INPUT               |

| - X      | MRITE INPUT              |

| 40 A1    | MORT ADDRESS             |

| /AT PAG  | PORT & (BIT)             |

| P87 P80  | PORT E (RIT)             |

| PC ? PCD | MORT CIRIT!              |

| VIC.     | 4 VCL15                  |

| SND      | # VO+ 11                 |

#### 8255A OPERATIONAL DESCRIPTION

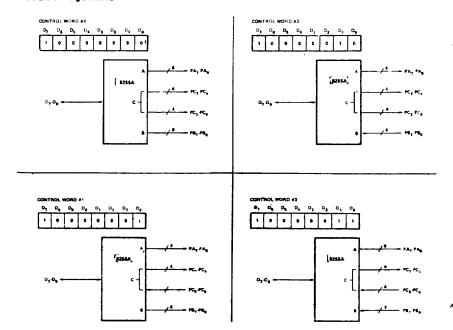

#### Mode Selection

There are three basic modes of operation that can be selected by the system software:

Mode 0 - Basic Input/Output

Mode 1 - Strobed Input/Output

Mode 2 - Bi-Directional Bus

When the reset input goes "high" all ports will be set to the input mode (i.e., all 24 lines will be in the high impedance state). After the reset is removed the 8255A can remain in the input mode with no additional initialization required. During the execution of the system program any of the other modes may be selected using a single output instruction. This allows a single 8255A to service a variety of peripheral devices with a simple software maintenance routine.

The modes for Port A and Port B can be separately defined, while Port C is divided into two portions as required by the Port A and Port B definitions. All of the output registers, including the status flip-flops, will be reset whenever the mode is changed. Modes may be combined so that their functional definition can be "tailored" to almost any I/O structure. For Instance; Group B can be programmed in Mode 0 to monitor simple switch closings or display computational results, Group A could be programmed in Mode 1 to monitor a keyboard or tape reader on an interrupt-driven basic

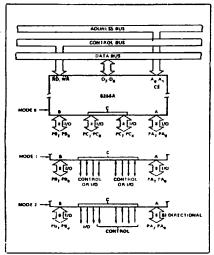

Figure 5. Basic Mode Definitions and Bus Interface

Figure 6. Mode Definition Format

The mode definitions and possible mode combinations may seem confusing at first but after a cursory review of the complete device operation a simple, logical 1/0 approach will surface. The design of the 8255A has taken into account things such as efficient PC board layout, control signal definition vs PC layout and-complete functional flexibility to support almost any peripheral device with no external ir gilc. Such design represents the maximum use of the available pins.

#### Single Bit Set/Reset Feature

Any, of the eight bits of Port C can be Set or Reset using a single OUTput Instruction. This feature reduces software requirements in Cohtrol-based applications.

Floure 7. Bit Set/Reset Format

When Port C is being used as status/control for Port A or 8, these bits can be set or reset by using the Bit Set/Reset operation just as if they were data output point.

#### Interrupt Control Functions

When the 8255A is programmed to operate in mode 1 or mode 2, control signals are provided that can be used as interrupt request inputs to the CPU. The interrupt request signals, generated from port C, can be inhibited or enabled by setting or resetting the associated INTE Itip floop, using the bit setreset function of port C.

This function allows the Programmer to disallow or allow a specific I/O device to interrupt the CPU without affecting any other device in the interrupt structure.

#### INTE flip-flop definition:

(BIT-SET) = INTE is SET - Interrupt enable

(BIT-RESET) - INTE is RESET - Interrupt disable

Note: All Mask flip-flops are automatically reset during mode selection and device Reset.

#### Operating Modes

MODE 0 (Basic Input/Output). This functional configuration provides simple input and output operations for each of the three ports. No "handshaking" is required, data is simply written to or read from a specified port

#### Mode D Basic Functional Definitions:

- Two 8-bit ports and two 4-bit ports.

- · Any portican be input or output.

- Outputs are latched.

- · Inputs are not latched.

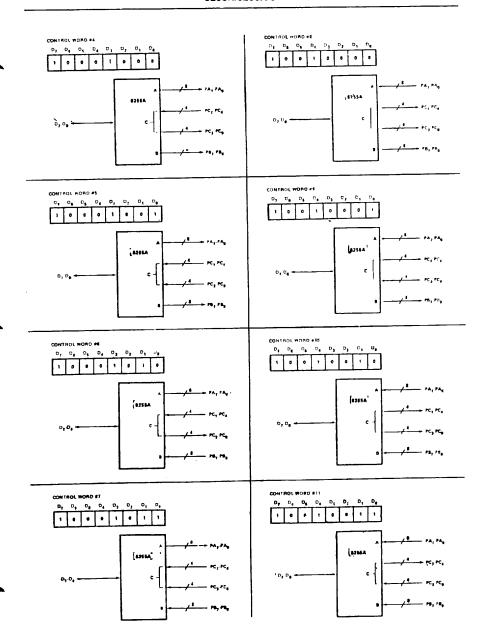

- 16 different Input/Output configurations are possible in this Mode.

#### MODE 0 (Basic Input)

MODE 0 (Basic Output)

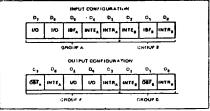

#### **MODE 0 Port Definition**

|    | A  |                | В  | GRO    | UP A              |    | GROUP B |        |  |

|----|----|----------------|----|--------|-------------------|----|---------|--------|--|

| D4 | D3 | D <sub>1</sub> | DO | PORT A | PORT C<br>(UPPER) | *  | PORT B  | PORT C |  |

| 0  | 0  | 0              | 0  | OUTPUT | OUTPUT            | 0  | OUTPUT  | OUTPUT |  |

| 0  | 0  | 0              | 1  | OUTPUT | OUTPUT            | 1  | OUTPUT  | INPUT  |  |

| 0  | 0  | 1              | 0  | OUTPUT | OUTPUT            | 2  | INPUT   | OUTPUT |  |

| 0  | 0  | 1              | 1  | OUTPUT | QUTPUT            | 3  | INPUT   | INPUT  |  |

| 0  | 1  | 0              | 0  | OUTPUT | INPUT             | 4  | DUTPUT  | OUTPUT |  |

| 0  | 1  | 0              | 1  | OUTPUT | INPUT             | 5  | OUTPUT  | INPUT  |  |

| 0  | ,  | 1              | 0  | OUTPUT | INPUT             | 6  | INPUT   | OUTPUT |  |

| 0  | 1  | 1              | 1  | OUTPUT | INPUT             | 7  | INPUT   | INPUT  |  |

| 1  | 0  | 0              | 0  | INPUT  | OUTPUT            | 8  | DUTPUT  | OUTPUT |  |

| 1  | 0  | 0              | 1  | INPUT  | OUTPUT            | 9  | OUTPUT  | INPUT  |  |

| 1  | 0  | 1              | 0  | INPUT  | OUTPUT            | 10 | INPUT   | OUTPUT |  |

| 1  | 0  | 1              | 1  | INPUT  | OUTPUT            | 11 | INPUT   | INPUT  |  |

| 1  | -  | 0              | 0  | INPUT  | INPUT             | 12 | OUTPUT  | OUTPUT |  |

| 1  | 1  | 0              | 1  | INPUT  | INPUT             | 13 | OUTPUT  | INPUT  |  |

| -  | 1  | 1              | 0  | INPUT  | INPUT             | 14 | INPUT   | OUTPUT |  |

| 1  | 1  | 1              | 1  | INPUT  | INPUT             | 15 | INPUT   | INPUT  |  |

#### MODE 0 Configurations

#### **Operating Modes**

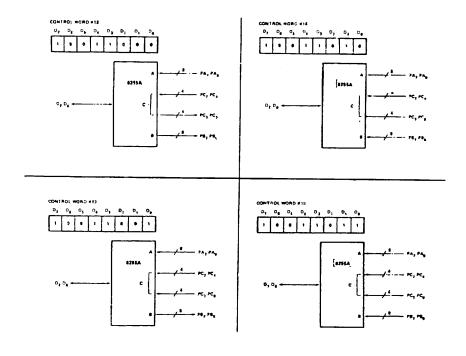

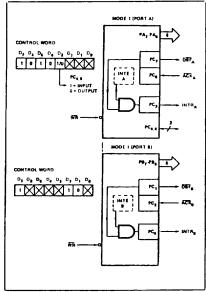

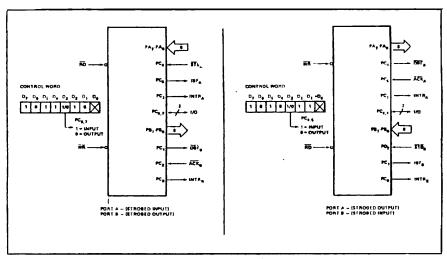

MODE 1 (Strobed Input/Output). This functional configuration provides a means for transferring I/O date to or from a specified port in conjunction with strobes or "handshaking" signals. In mode 1, port A and Port B use the lines on port C to generate or accept these "handshaking" signals.

#### Mode 1 Basic Functional Definitions:

- Two Groups (Group A and Group B)

- Each group contains one 8 bit data port and one 4-bit control/data port.

- The 8-bit data port can be either input or output.

Both inputs and outputs are latched.

- The 4-bit port is used for control and status of the 8-bit data port

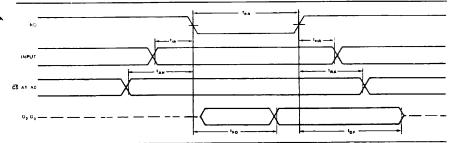

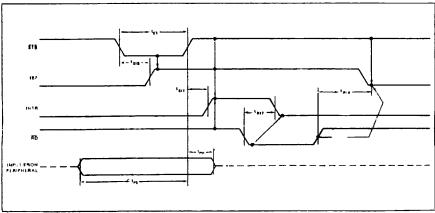

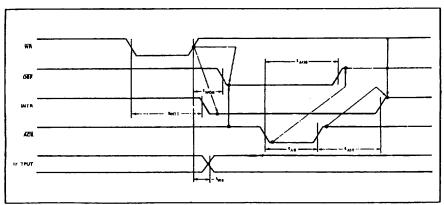

#### Input Control Signal Definition

STB (Strobe Input), A "low" on this input loads data into the input latch.

#### IBF (Input Buffer Full F/F)

A "high" on this output Indicates that the data has been loaded into the input latch; in essence, an acknowledgement IBF is set by STB input being low and is reset by the rising edge of the RD input.

#### **INTR** (Interrupt Request)

A "high" on this output can be used to interrupt the CPU when an input device is requesting service. INTR is set by the STB is a "one", IBF is a "one" and INTE is a "one". It is reset by the falling edge of RD. This procedure allows an input device to request service from the CPU by simply strobing its data into the port.

INTE A

Controlled by bit set/reset of PC<sub>4</sub>.

INTE B

Controlled by bit set/reset of PC<sub>2</sub>.

Figure 8. MODE 1 input

Figure 9. MODE 1 (Strobed Input)

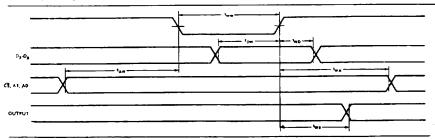

#### **Output Control Signal Definition**

OBF (Output Buffer Full F/F). The OBF output will go "low" to indicate that the CPU has written data out to the specified port. The OBF F/F will be set by the rising edge of the WR input and reset by ACK input being low.

ACK (Acknowledge Input). A "low" on this input informs the 8255A that the data from port A or port B has been accepted. In essence, a response from the peripheral device indicating that it has received the data output by the CPU.

INTR (Interrupt Request). A "high" on this output can be used to interrupt the CPU when an output device has accepted data transmitted by the CPU. INTR is set when ACK is a "one", OBF is a "one" and INTE is a "one". It is reset by the falling edge of WR.

INTE A

Controlled by bit set/reset of PCs.

INTE B

Controlled by bit set/reset of PC 2.

Figure 10. MODE 1 Output

Figure 11, Mode 1 (Strobed Output)

#### Combinations of MODE 1

Part A and Port B can be individually defined as input or output in Mode 1 to support a wide variety of strobed I/O applications.

Figure 12. Combinations of MODE 1

#### Operating Modes

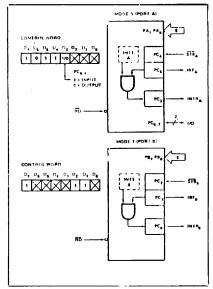

MODE 2 (Strobed Bidirectional Bus I/O). This functional configuration provides a means for communicating with a peripheral device or structure on a single 8-bit bus for both transmitting and receiving data (bidirectional bus I/O). "Handshaking" signals are provided to maintain proper bus flow discipline in a similar manner to MODE 1, interrupt generation and enable/disable functions are also available.

MODE 2 Basic Functional Definitions:

- · Used in Group A only.

- One 8-bit, bl-directional bus Port (Port A) and a 5-bit control Port (Port C).

- Both Inputs and outputs are latched.

- The 6-bit control port (Port C) is used for control and status for the 8-bit, bi-directional bus port (Port A).

#### Bidirectional Bus I/O Control Signal Definition

INTR (interrupt Request). A high on this output can be used to interrupt the CPU for both input or output operations.

#### **Output Operations**

OBF (Output Buffer Ful). The OBF output will go "low" to indicate that the CPU has written data out to port A.

ACK (Acknowledge). A "low" on this input enables the tri-state output buffer of port A to send out the data. Otherwise, the output buffer will be in the high impedance state.

INTE 1 (The INTE Filip-Fiop Associated with OBF), Controlled by bit settreset of PCs.

#### Input Operations

STB (Strobe Input)

STB (Strobe Input). A "low" on this input loads data into the Input latch.

IBF (input Buffer Full FIF). A "high" on this output indicates that data has been loaded into the input latch.

INTE 2 (The INTE Filp-Flop Associated with IBF). Controlled by bit set/reset of PC...

#### Mode Definition Summary

|                 | MC   | DDE 0 | 7 | MC           | DE 1  | 7   | MODE 2       | ]   |         |

|-----------------|------|-------|---|--------------|-------|-----|--------------|-----|---------|

|                 | IN   | OUT   | ] | IN           | OUT   | 1   | GROUP A DNLY | 1   |         |

| PAO             | IN   | OUT   | 1 | IN           | OUT   | 1   | <del></del>  | 1   |         |

| PAI             | IN   | оит   | 1 | IN           | OUT   | ı   | ◄            | 1   |         |

| PA <sub>2</sub> | IN   | OUT   | 1 | IN           | OUT   | 1   | <b>→</b>     |     |         |

| FA3             | 1N   | OUT   |   | IN           | OUT   |     | <b>→</b>     | l   |         |

| PA <sub>4</sub> | IN   | OUT   | 1 | IN           | out   | 1   |              | İ   |         |

| PAS             | iN   | OUT   |   | IN           | OUT   | 1   | <b></b>      | 1   |         |

| PAg             | IN   | OUT   |   | IN           | OUT   | 1   | <b>←</b>     | l   |         |

| PA7             | IN   | OUT   | 1 | IN           | OUT   |     | <b>◄</b>     | l   |         |

| PB <sub>0</sub> | IN   | OUT   | 1 | IN           | OUT   | 1   |              |     |         |

| PB 1            | IN   | 007   |   | IN           | OUT   |     |              | 1 1 |         |

| P82             | IN   | OUT   |   | IN           | OUT   | Į.  | l —          | 1 1 |         |

| reg             | IN   | OUT   |   | IN           | DUT   |     | <del></del>  |     | MODE 0  |

| P84             | IN   | יטם   |   | IN           | OUT   | l l |              | l l | 300M RO |

| P8 <sub>5</sub> | IN   | OU.   |   | IN           | OUT   | 1   |              | l   | ONLY    |

| ₽B6             | IN   | 001   | ļ | iN           | 700   |     |              |     |         |

| PB7             | IN . | DUT   | 1 | IN           | our   |     |              |     |         |

| PCo             | IN   | OUT   | 1 | INTRB        | INTRB |     | 1/0          | _   |         |

| PC <sub>1</sub> | IN   | ουτ   |   | 187 <b>a</b> | ÖBF8  |     | 1/0          |     |         |

| PC <sub>2</sub> | IN:  | OUT   |   | ST B B       | ACKE  | l . | 1/0          | 1   |         |

| PC3             | IN   | , out |   | INTRA        | INTRA |     | INTRA        | İ   |         |

| PC4             | IN   | OUT   |   | STBA         | 1/0   |     | STBA         | ı   |         |

| PC <sub>6</sub> | IN   | our   |   | IBFA         | 1/0   |     | IBFA         | Ī   |         |

| PCe             | IN   | OUT   |   | 1/0          | ACKA  | 1   | ACK A        | l   |         |

| PC7             | IN   | OUT   |   | 1/0          | CBFA  |     | ŌBF A        |     |         |

#### Special Mode Combination Considerations

There are several combinations of modes when not all of the bits in Port C are used for control or status. The remaining bits can be used as follows:

#### If Programmed as Inputs -

All Input lines can be accessed during a normal Port C read

#### If Programmed as Outputs -

Bits in C upper (PC<sub>7</sub>-PC<sub>4</sub>) must be individually accessed using the bit set/reset function.

Bits in C lower (PC<sub>3</sub>-PC<sub>0</sub>) can be accessed using the bit set/reset function or accessed as a threesome by writing into Port C.

#### Source Current Capability on Port B and Port C

Any set of eight output buffers, selected randomly from Ports B and C can source ImA at 1.5 volts. This feature allows the 8255 to directly drive Darlington type drivers and high-voltage displays that require such source current.

#### Reading Port C Status

In Mode 0, Port C transfers data to or from the peripheral device. When the 8255 is programmed to function in Modes 1 or 2, Port C generates or accepts "hand shaking" signals with the peripheral device. Reading the contents of Port C

allows the programmer to test or verify the "status" of each peripheral device and change the program flow accordingly.

There is no special instruction to read the status information from Port C, A normal read operation of Port C is executed to perform this function.

Figure 17. MODE 1 Status Word Format

Figure 18. MODE 2 Status Word Format